Institute for Advanced Study Math. - Nat. Sci. Library Princeton, N. J. 08540

Ins. H ) "ECP Interim ...

SUCULD

INTERI, FROCESS REFORT

OA THE

PHYSICAL REALIZATION OF AN

ELECTRONIC CO. PUTTUC 1 STREET

Ву

Julian H. Bigelow

Theodore ... ifildebrandt

James H. Pomerene

Richard L. Snyder

Ralph J. Slutz

Willis F. Ware

Institute for Advanced Study

1 July 1947

IAS ECP list of reports, 1946-57. no. 5.

### PREFACE

The ensuing interim report has been prepared in accordance with the terms of Contract W-36-034-CRD-7481 between Research and Development Service, Ordnance Department, U. S. Army and the Institute for Advanced Study. The express purpose of this report is to furnish contemporary advice to the Service regarding steps taken and contemplated toward the realization of an electronic computing instrument embodying the principles outlined in the following Institute for Advanced Study reports:

23 June 1946, by Burks Goldstine and von Neumann entitled, "Preliminary Discussion of the logical Design of an Electronic Computing Instrument." (Hereinafter referred to as L.D. 1).

1 April 1947, by Goldstine and von Neumann entitled, "Planning and Coding of Problems for an Electronic Computing Instrument". (Hereinafter referred to as F.C. 1).

The present report on the Physical Realization of the Computer is to be considered as a continuation of that listed above under the same title and employs the same nomenclatures and organizational plan.

The closing date of this installment -- 1 July 1947 -- finds the development group at the midpoint in soveral fundamental enterprises, and accordingly no attempt is made to present an integrated and comprehensive discussion of the entire problem of realization. Where specific progress has been made on various organs and components a orief account is given to convey the main facts; non-critical and transient detail being avoided whenever possible.

\_\_\_\_\_

The experimental techniques, component types, schemes for synthesis of primary organs as well as the underlying philosophy of realization indicated in this report should be understood as wholly tentative, and are subject to revision from time to time either in detail or in their entirety as the work progresses.

J. fi. B.

T. W. B.

J. H. F.

R. L. S.

R. J. S.

W. H. W.

## TABLE OF CONTENTS

| ı.    | RIMARKS ON ORGANIZATION                               | Page | 1  |

|-------|-------------------------------------------------------|------|----|

| II.   | GENERAL DISCUSSION OF COMPUTER                        | Page | 2  |

| III.  | REMARKS ON THE REALIZATION OF LARGE MEMORY CAPACITY , | Page | 2  |

| IV.   | MAGNETIC RIBBON EXPLORATION: TEST APPARATUS.          | Page | 2  |

| ٧.    | MAGNETIC RIBBON EXPLORATION: PERFORMANCE STUDIES      | Page | 3  |

| VI.   | OUTER MEMORY COMPONENT (M2) DESIGN STUDIES            | Page | 13 |

| VII.  | INPUT-OUTPUT TRANSCRIBER SYSTEM                       | Page | 17 |

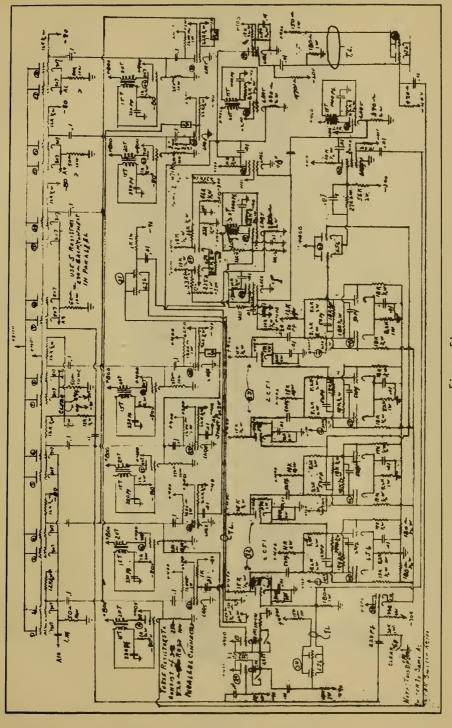

| viii. | BINARY ELEMENTS: TEST APPARATUS                       | Page | 26 |

| IX.   | BINARY ELEMENT PERFORMANCE STUDIES                    | Page | 30 |

| X.    | REGISTER COMPONENT STUDIES                            | Page | 33 |

| XI.   | ACCUMULATOR COMPONENT STUDIES                         | Page | 38 |

| XII.  | CONTROL COMPONENT STUDIES                             | Page | 45 |

# FIGURES

| No.    | Description                                                   | Page       |

|--------|---------------------------------------------------------------|------------|

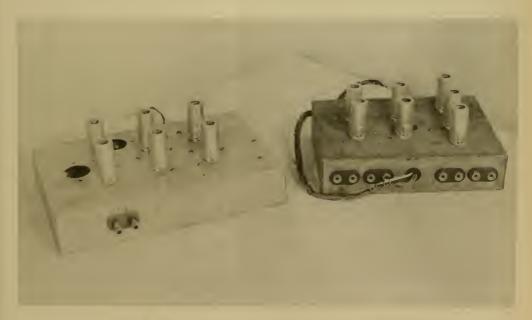

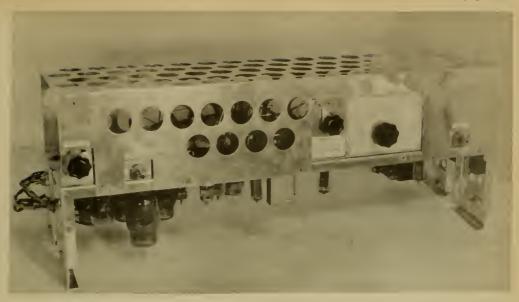

| 1      | Low Speed Loop Sample Comparator, Mod 2                       | 3A         |

| 2      | Special Transmitter Distributor                               | 3A         |

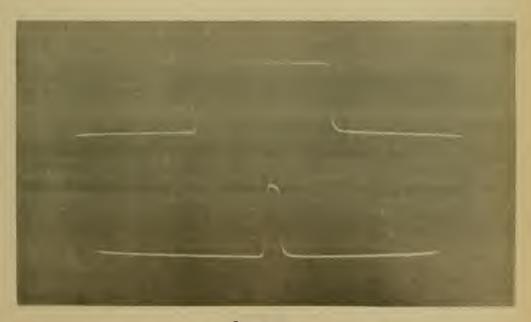

| 3      | Recording Head Output Voltages                                | A8         |

| 4A     | Adjacent Voltage Pulses of Opposite Sign                      | 8B         |

| 4B     | Adjacent Voltage Pulses of Opposite Sign when 50%             |            |

|        | Amplitude Interference Occurs                                 | 8B         |

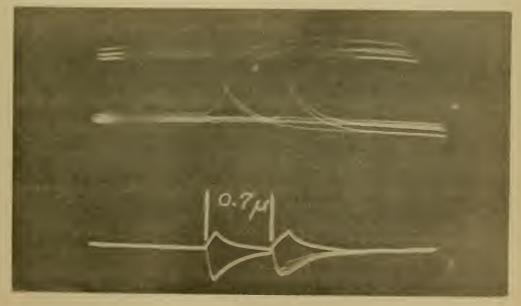

| 5A,B,C | Magnetic Wire Reproduced Wave Forms                           | 8C         |

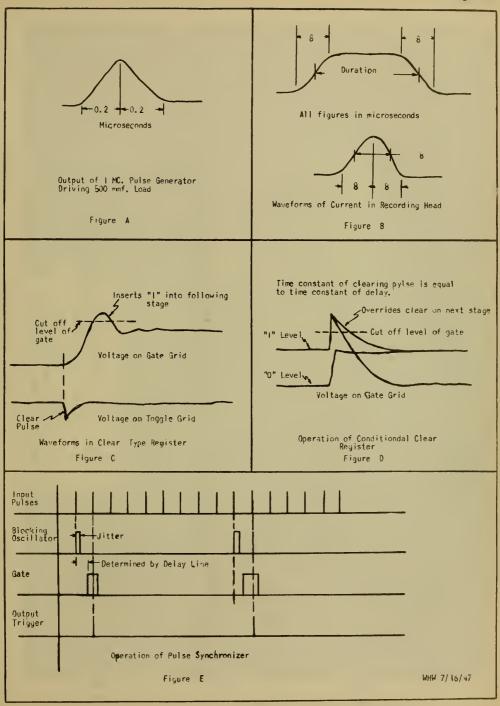

| 6A-E   | Register and Synchronizer Wave Forms                          | 9A         |

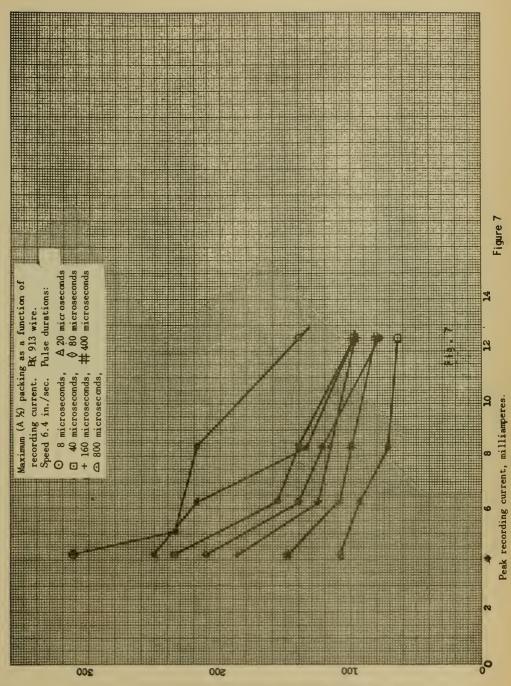

| 7      | Packing versus Recording Current - Curve                      | 9B         |

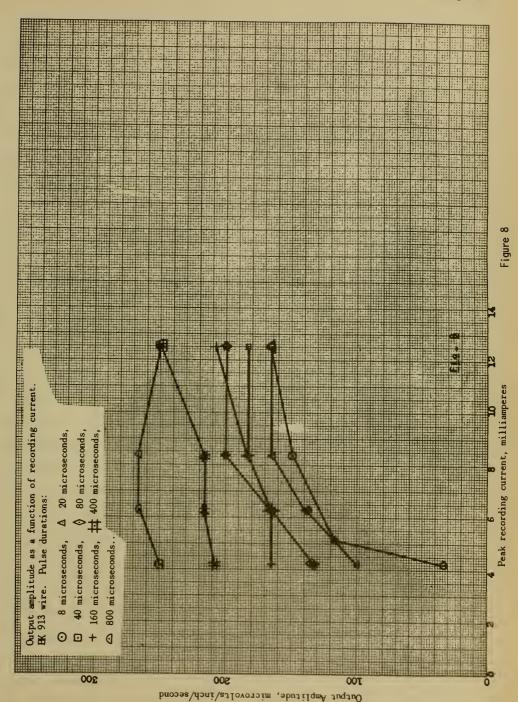

| 8      | Output versus Recording Current - Curve                       | 90         |

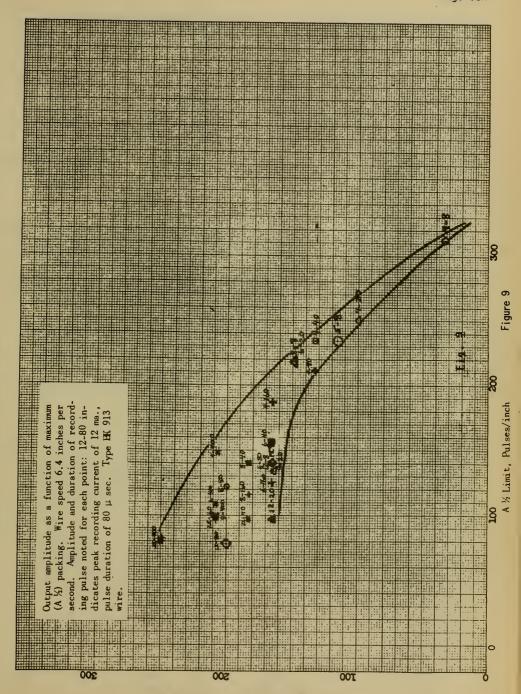

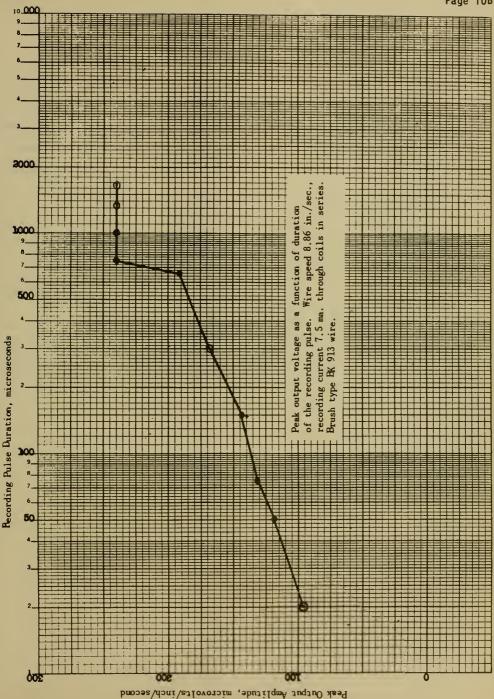

| 9      | Output versus Packing - Curve                                 | 10A<br>10B |

| 10     | Output versus Duration - Curve                                |            |

| 11A    | Plate Model, M-2 Wire Drive showing Level Winder              | 13A        |

| 118    | Plate Model, M-2 Wire Drive showing Experimental Differential | 13A        |

| 13     | (No Figure 12) Model 1 Wire Drive Unit                        | 15B        |

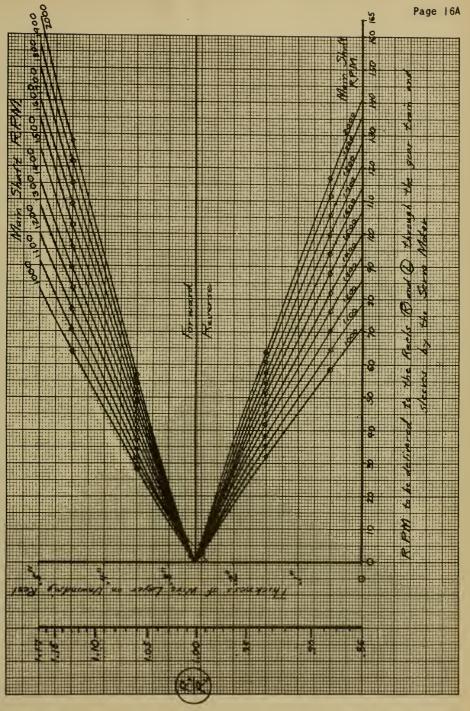

| 14     | Wire Drive Servo Requirements                                 | 16A        |

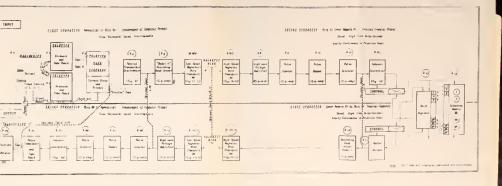

| 15     | Block Diagram of Input-Output Circuits                        | 20A        |

| 16     | Voltage Preamplifier                                          | 21A        |

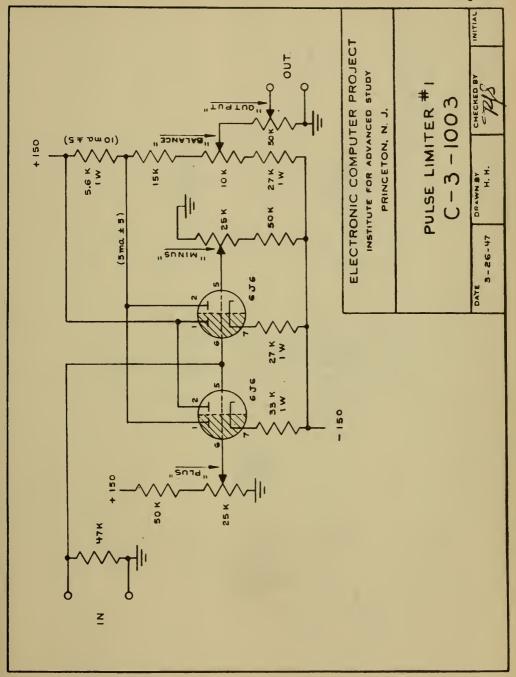

| 17     | Pulse Limiter                                                 | 21A        |

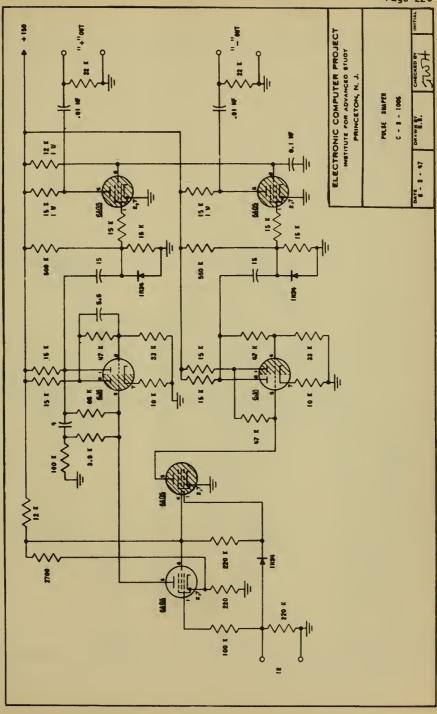

| 18     | Pulse Shaper                                                  | 21A        |

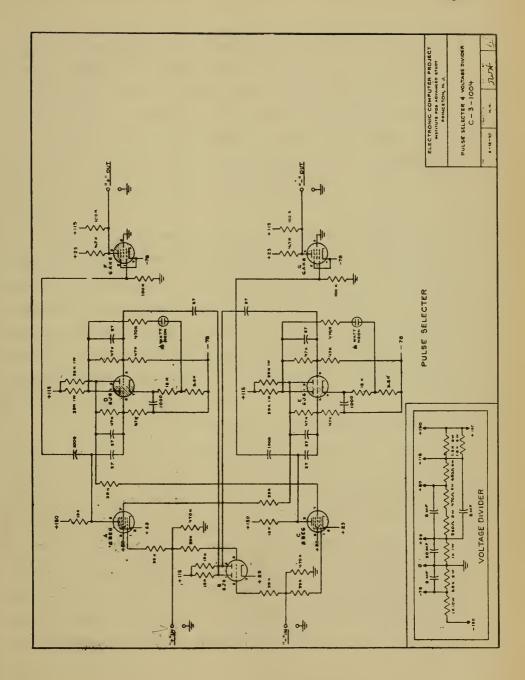

| 19     | Pulse Selector                                                | 21A        |

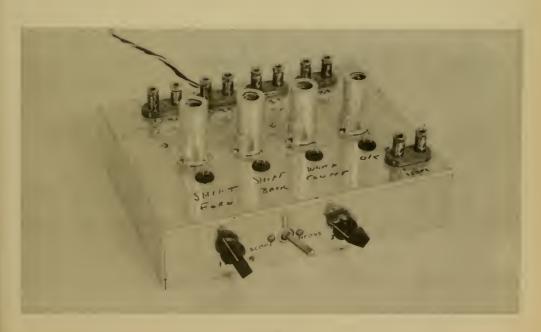

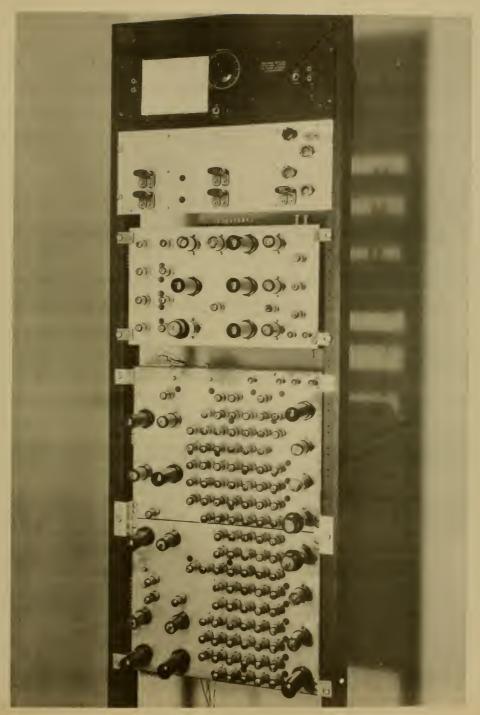

| 20     | Indexer-Interpreter, Chassis II                               | 22A        |

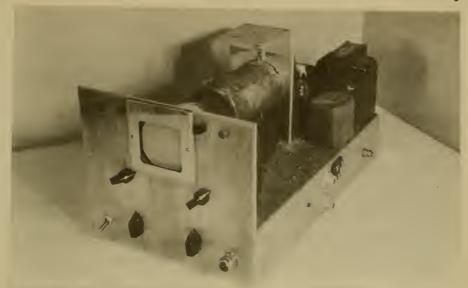

| 21     | Pulse Viewer                                                  | 22A        |

| 22     | Input Circuits                                                | 25A        |

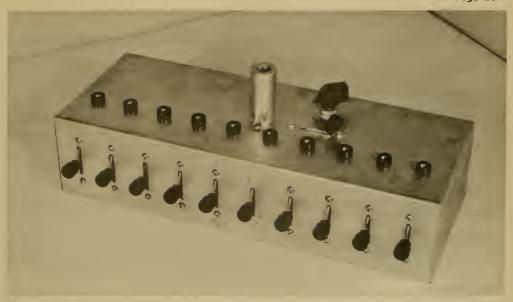

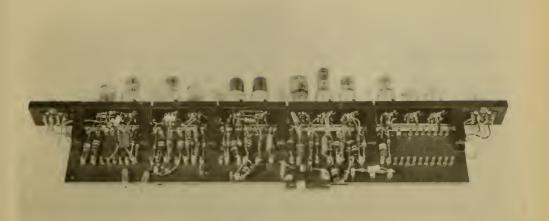

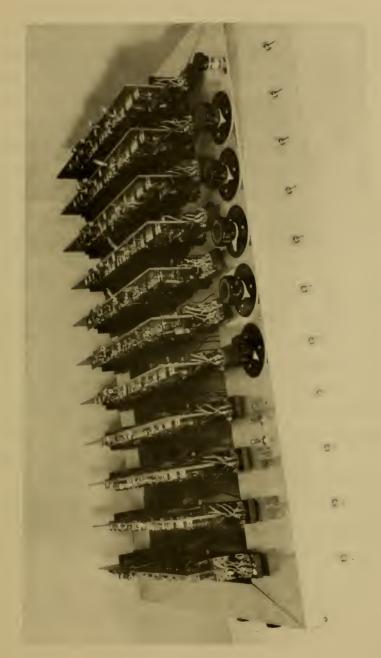

| 23     | Ten output pulse Generator, Chassis                           | 26A        |

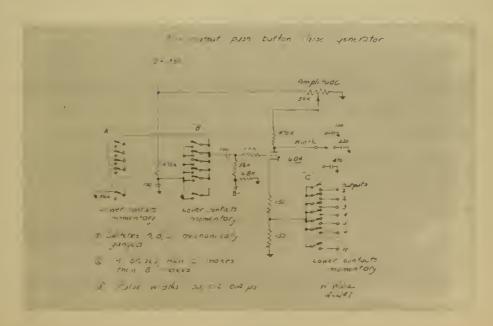

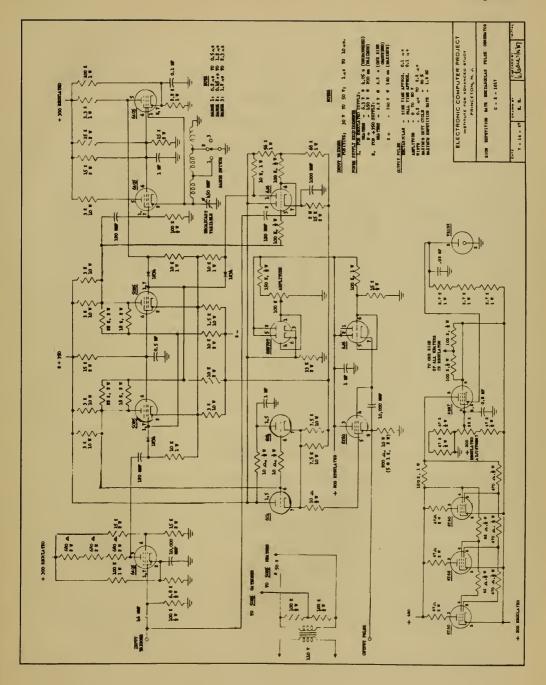

| 24     | Ten output pulse Generator, Diagram                           | 26A        |

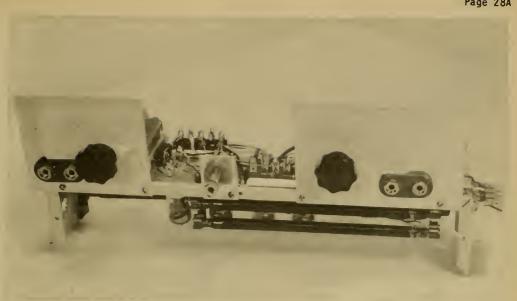

| 25     | Dual Whisker Generator                                        | 28A        |

| 26     | Pulse Synchronizer                                            | 28A        |

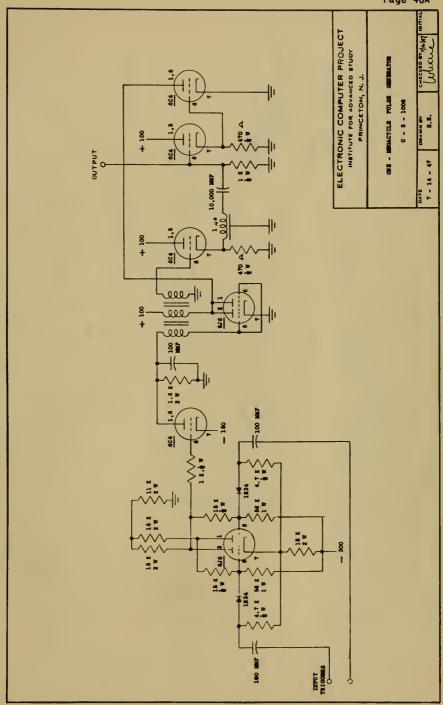

| 27     | Variable Parameter Megacycle Pulse Generator                  | 27B        |

| 28     | Variable Parameter Megacycle Pulse Generator Performance      | 27B        |

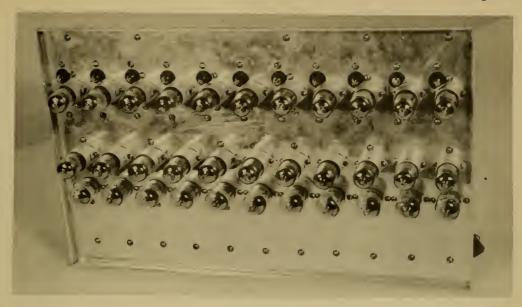

| 29     | Single Channel of Accumulator Component                       | 27C        |

| 30     | Chassis for Experimental Circuits                             | 27C        |

| 31     | Single Trace Long Persistence C. R. O.                        | 270        |

| 32     | Pulse Repetition Rate Indicator                               | 27D        |

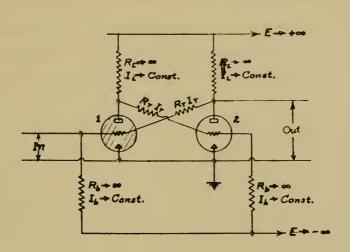

| 33     | Binary Toggle - Degenerate                                    | 31A        |

| 34     | Binary Toggle: Arbitrary Sensitivity Ratio (No Figure 35)     | 31A        |

# FIGURES (cont.)

| Figure<br>No.        | Description                                                                       | Page       |

|----------------------|-----------------------------------------------------------------------------------|------------|

| 36                   | Cathode Coupled Toggle                                                            | 32A        |

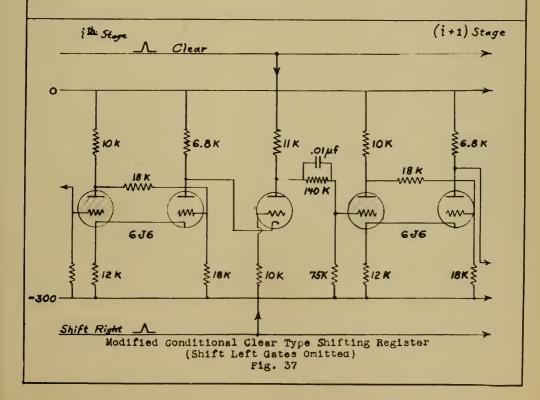

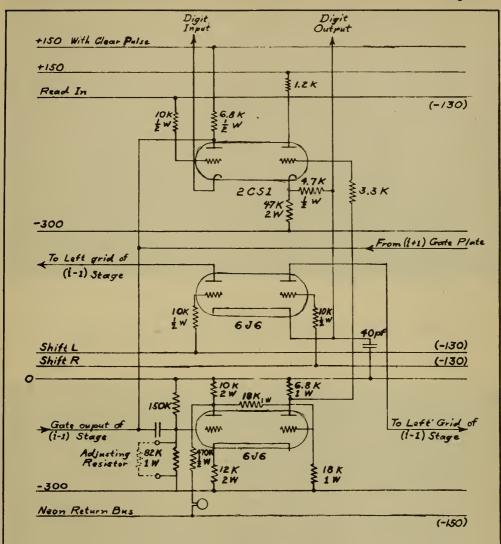

| 37                   | Modified Conditional Clear Type Shifting Register                                 | 32A        |

| 38                   | Conditional Clear Type Shifting Register                                          | 34A        |

| 39                   | Shifting Register Performance                                                     | 34B        |

| 40                   | Shifting Register Performance                                                     | 34B        |

| 41                   | Modified Clear Type Shifting Register                                             | 34C        |

| 42                   | Modified Clear Type Shifting Register                                             | 34C        |

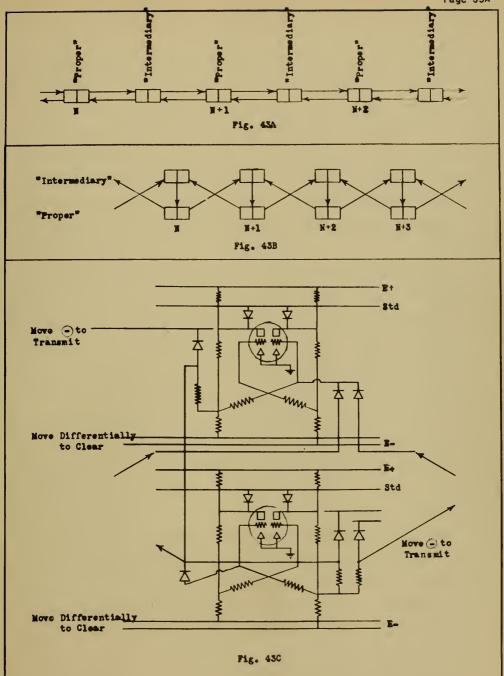

| 43A,B,C              | Block Diagram of Positive Interlock Shifting Register                             | 35A        |

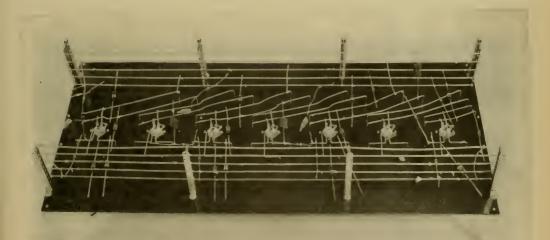

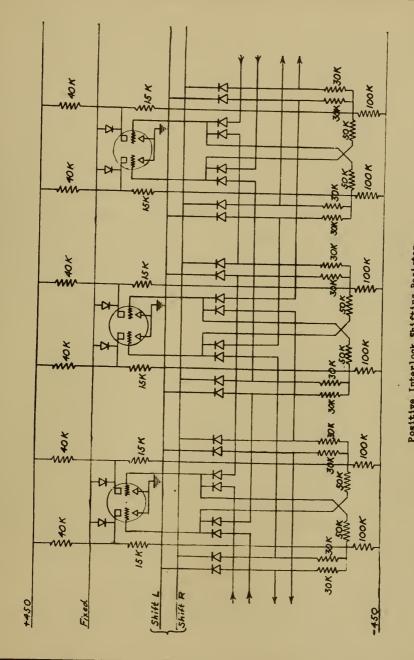

| 44                   | Positive Interlock Shifting Register                                              | 37A        |

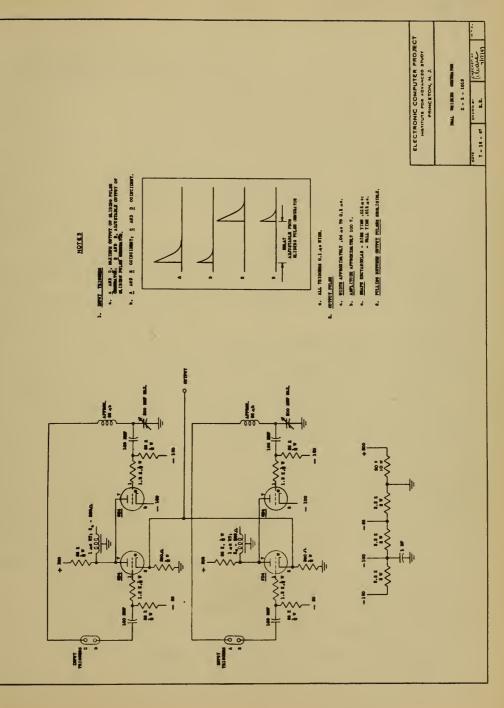

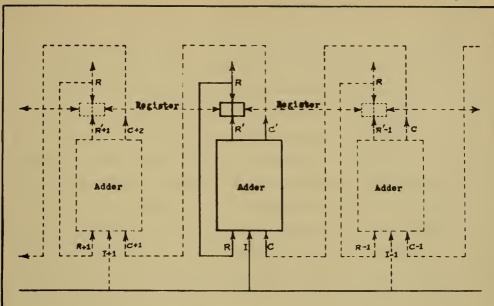

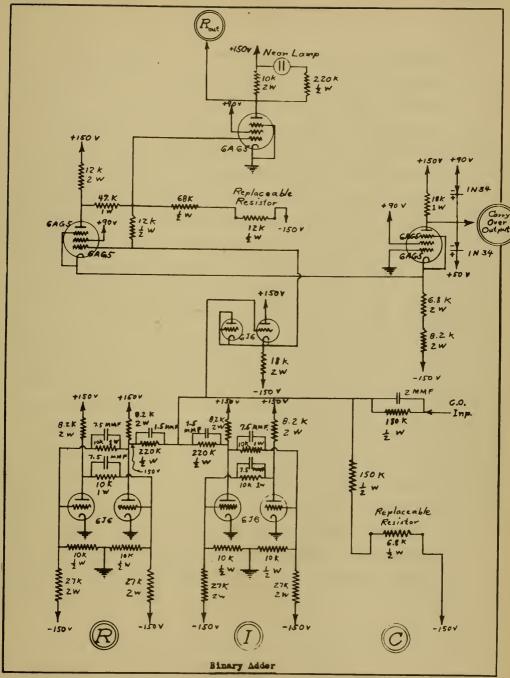

| 45A                  | Adder Schematic                                                                   | 38A        |

| 45B                  | The Adder Problem                                                                 | 38A        |

| 46A                  | Adder                                                                             | 40A        |

| 46B                  | Adder                                                                             | 40A        |

| 47                   | Binary Adder                                                                      | 40B        |

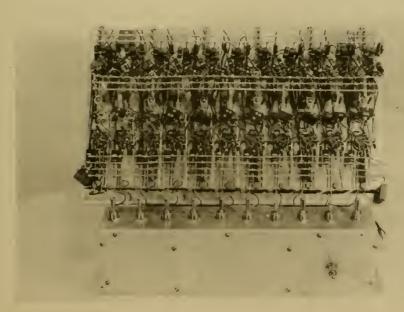

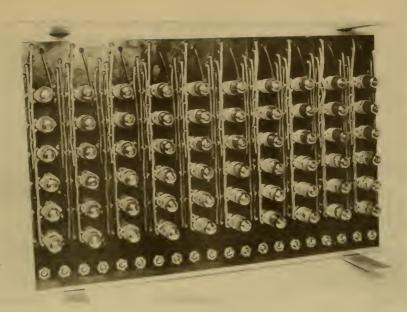

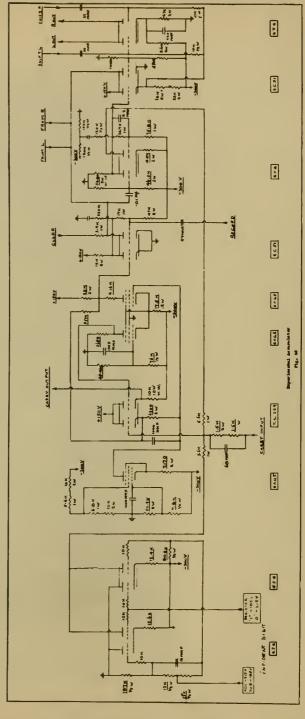

| 48                   | Experimental Accumulator                                                          | 43A        |

| 49<br>50             | Eleven stage Binary Accumulator                                                   | 43B        |

| 51                   | Schematic of Experimental Multiplier Control                                      | 48A<br>48B |

| 52                   | Multiplier Control Circuit, Experimental Multiplier Control Chassis, Experimental | 48C        |

|                      | DRAWINGS                                                                          |            |

|                      |                                                                                   |            |

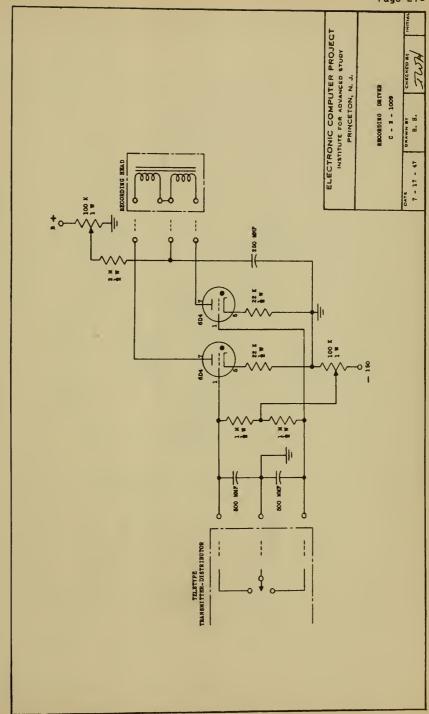

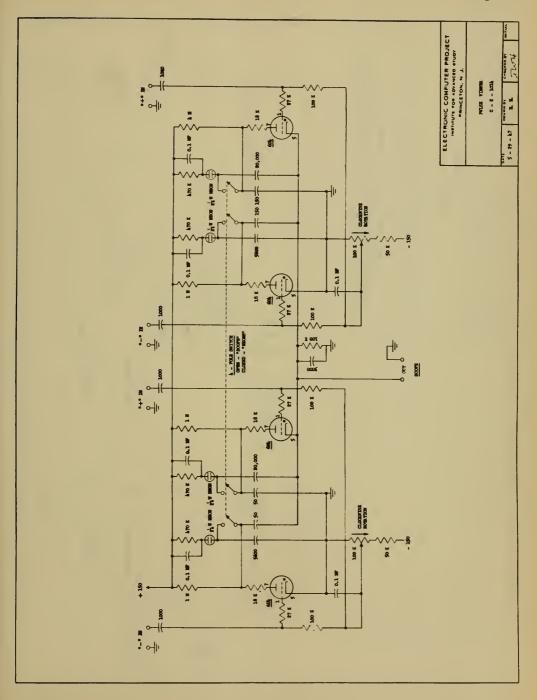

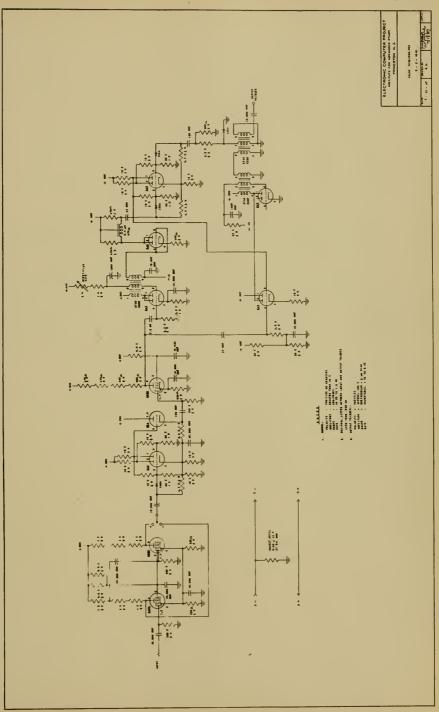

| 0-3-1009             | Recording Driver                                                                  | 21B        |

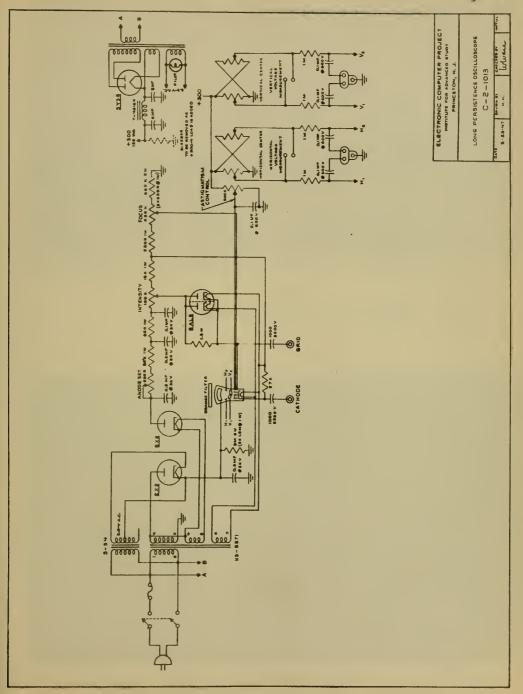

| C-2-1014             | Pulse Viewer                                                                      | 210        |

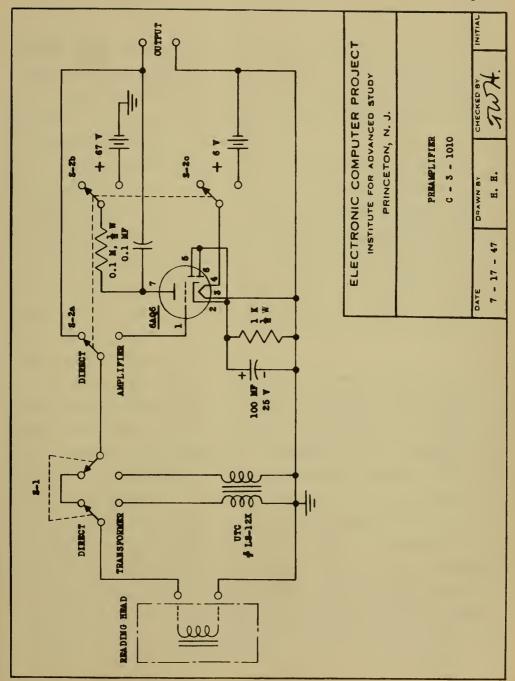

| C-3-1010             | Preamplifier                                                                      | 21 D       |

| 0-3-1003             | Pulse Limiter No. 1                                                               | 22B        |

| C-3-1005             | Pulse Shaper                                                                      | 220        |

| C-3-1004             | Pulse Selector and Voltage Divider                                                | 22D        |

| C-3-1007             | Recording Driver, Model 1                                                         | 24A        |

| C-2-1013             | •                                                                                 | 27A        |

| C-2-1016             | Pulse Synchronizer                                                                | 28B<br>29A |

| C-2-1018             |                                                                                   | 29A<br>46A |

| C-3-1008<br>C-2-1017 | One Megacycle Pulse Generator High Repetition Rate Rectangular Pulse Generator    | 46B        |

| 0-2-1017             | nigh Repetition Rate Rectangular Fulse Generator                                  | 405        |

|                      | TABLES                                                                            |            |

| 1                    | Output versus Speed                                                               | 6          |

| 2                    | Comparative Tests of Magnetic Wire                                                | 12         |

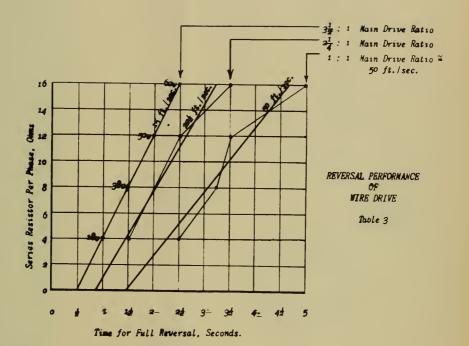

| 3                    | Reversal Performance of Wire Drive                                                | 15A        |

#### I. REMARKS ON ORGANIZATION

In January, 1947, the development group moved to its new quarters in the computer building, where many facilities became available. A small but adequate model machine-shop was set up, including a vertical and a horizontal milling machine, a surface grinder, small crank shaper, a medium and a small screw-cutting lathe, drill presses, welding bench, spotwelder, sheet metal brake and shear, etc. The shop model-making staff was increased to two when Mr. John Van Pelt joined our group; this arrangement has resulted in a very efficient and flexible unit, and is expected to continue. Two experienced wiring technicans, Mr. Lacey and Mr. Fell, constitute the electrical construction unit, and space is provided for several semi-skilled workers in uniticipation of multiple assembly work of full-scale construction. The entire construction group of four is under the supervision of a production engineer, Mr. Richard Melville.

In February, 1947, two research engineers joined the group:

Mr. Theodore Hildebrandt as a permanent addition, and Mr. Richard Snyder

who remains with the group until September 1947. The engineering staff

is consequently restored to the original quota of six, and was greatly

strengthened by this addition.

The new building has provided adequate office space, conference room, drafting room, etc., and is considered to have been a great advantage.

#### II, GENERAL DISCUSSION OF COMPUTER

No essentially new ideas or changes of those presented in the earlier report have developed. It should be re-emphasized that the present limited objective of the development group is to produce at an early date what may be called a primitive model of the computer, having control features of less than optimum convenience. To this end several of the organs and components have been forwarded along lines of development less concise and more conventional than those indicated in section II of the report (P.R. 1) with a view toward advancing the date of primitive operation.

#### III. REMARKS ON THE REALIZATION OF LARGE MEMORY CAPACITY

No attempt has been made to advance in this direction since the January 1 report, except for certain tests and developments on magnetic wire recording, reported under section 5.

### IV. MAGNETIC RIBBON EXPLORATION: TEST APPARATUS

#### 4.1 LOOP SAMPLE COMPARATOR.

It may be recalled that this apparatus consists of a two-speed phonograph motor arranged to drive a loop specimen of magnetic recording wire (held in tension by a weight) over various recording heads. The speeds at which this apparatus was originally capable of operating ranged from one-half to several feet per second. However, experimental work in connection with the teletype input and output transcriber components (see Section VII) created a need for lower speeds; in particular, for speeds as low as one-tenth inch per second (two typed characters per second). Accordingly the apparatus was provided with a gear reduction to change

the time scale, and other mechanical improvements as indicated by Figure 1.

- 4.3 HIGH SPRED MECHANICAL DRIVE TESTER: FOR DEVELOPMENTS SEE SECTION VI: "OUTER MEMORY COMPONENT DESIGN STUDIES".

- 4.4 RECORDING-HEAD BOOSTER AMPLIFIER: FOR DEVELOPMENTS SEE SECTION VII: "INPUT-OUTPUT TRANSCRIBER COMFONENT STUDIES".

#### V. MAGNETIC RIBBON EXPLORATION: FERFORMANCE STUDIES

5.1 and 5.2 MAGNETIC PERFORMANCE AS FUNCTION OF SPEED.

As discussed in P.R. -1 under the above numbered sections, the primitive model computer must be able to record and reproduce pulse data on magnetic wire on both typewriter speeds (about 1 inch-second) and at "electronic speeds" (about 600 inches/second). However, in the primitive model computer it is planned to restrict the operation so that recording of typed (legible) characters onto the wire and their reproduction there from will be carried out only in uninterrupted runs from prepunched teletype tape (See section 7 to follow). Also, it is planned to load and unload the inner electronic memory (N<sub>1</sub>) by means of the high speed wire drive outer memory (N<sub>2</sub>) in uninterrupted runs at essentially constant speed (See Section 6 to follow). These two restrictions will result in a relatively clumsy mode of operation of the primitive computer, and will be wasteful of wire capacity as well as operating time. However, their disadvantages are considered temporarily tolerable in view of the many consequent simplifications and short-cuts in the apparatus.

Specifically, the continuous-run full speed exchange of data between M<sub>1</sub> and M<sub>2</sub> will permit the use of essentially simpler continuous speed single purpose mechanical drives in M<sub>2</sub> and also a simple low speed drive for

Figure | Low Speed Loop Sample Comparator, Mod 2

Figure 2 Special Transmitter Distributor

use with the teletype transcribing component. Furthermore, this restricted operation of the primitive model computer will permit construction of (essentially simple) single purpose electrical channels suitable only for the voltages produced at the two particular speeds selected. Other advantages accrue and will be discussed elsewhere.

However, this restricted mode of operation must eventually be obviated in any adequate model of the computing machine. The outer memory (M2) must in the final model be automatically at the command of the control organ, being able to start, stop, reverse-and-hunt, etc., as the occasion demands. This will require complete speed flexibility of the drive system and electrical channels associated with Ma; and in particular the reversal requirement demands that the single electrical channel associated with M2 must be able to handle with certainty wire voltage outputs corresponding to a speed range from 600 inches por second to as near zero as possible, This lower limit of speed (at which reading must still be possible) may be estimated by a crude calculation, based on the fact that at this minimum reading speed it must be possible to halt the rotation of the drive system within one-half word lengths on the wire; in order not to lose place. The closest packing now contemplated is two words (110 binary characters, including markers; see P.R.-1, section 7) per inch, so that the requirement is that the drive be halted within 1/4 inch, from minimum reading velocity. Using the relationship  $g = V^2/2S$  it is trivial to calculate that if minimum reading velocity is one inch per second, about one-sixth gravity is needed to stop in a quarter inch. while if minimum reading velocity is ten inches per second, about sixteen times gravity is required. hence, if the electrical channel assoicated with the high speed drive system can operate reliably on voltage outputs corresponding

s de  $d_{-1}=j$

to two or three inches per second, the problem of preserving index through reversal of the wire drive presents no serious difficulty. Since reading at these low speeds is known to be feasible (see Section 5 of P.R.-1, also later sections of present report) no fundamental obstacle is to be anticipated when the automatic M<sub>2</sub> control is appended to the M<sub>2</sub> wire drive.

Some rough consideration should be given the problem of designing the electrical channel to be associated with the automatic M<sub>2</sub> in order to anticipate any difficulties that may arise. Conceivably, an electrical system could be designed which would operate on all electrical voltage outputs from the wire reading head, regardless of their amplitude, provided it exceed a certain predetermined minimum. Such a system would have in an early stage a purely binary cell, capable of producing at its output terminals a standardized "count" signal for any input pulse regardless of scale factor, provided only that it exceed threshold. In such a scheme, a fixed ratio amplification system could in principle be used for all reading spe@ds.

However, in considering such a scheme, the signal to noise ratio of the voltage output from the reading head must be taken into account. This ratio may remain nearly constant though both signal and noise voltage increase with speed, and in fact the noise level may be relatively higher at high speeds. Hence for a speed range of about 10<sup>3</sup> the hoise at high speed may be expected to exceed the signal at low speed, so that a fixed voltage threshold binary counter would almost certainly be unsuitable. Accordingly, some means of introducing voltage gain correction in the amplifier channel (as a function of velocity)must be considered. This might be effected by a voltage takeoff tachometer on the wire drive system, arranged to introduce a linear term in the amplifier gain.

----

Accordingly, although the problem is not immediate, it was considered desirable to obtain a rough picture of how the peak voltage output of one or two representative magnetic wires would vary with speed, and whether normalization by a linear velocity term would produce a fairly constant scale factor. A few simple tests of this sort were carried out, using square wave inscription pulses, being careful to provide ample geometric spacing to keep overlap effects from being significant, and using frequencies thought to be well within the capabilities of the recording head. The results, normalized according to wire speed, are indicated in Table 1 below:

TABLE I

| Wire<br>Type   | Speed in/sec. | Square wave cycles/inch | Output, average to peak uv/in/sec |

|----------------|---------------|-------------------------|-----------------------------------|

| B <b>K</b> 915 | 0.37          | 19.7                    | 143                               |

|                | 0.865         | 19.7                    | 171                               |

|                | 8.86          | 19.7                    | 178                               |

|                | 20.8          | 19.7                    | 171                               |

| S 6828         | 0.37          | 19.7                    | 47.5                              |

|                | 0.865         | 19.7                    | 67                                |

|                | 8.86          | 19.7                    | 74                                |

|                | 20.8          | 19.7                    | 72.5                              |

|                | 600.          | 1.67                    | 92.5                              |

and appear to show that peak voltage output is roughly proportional to speed of the reproducing wire. The approximate constancy of the normalized voltage peak may be less valid for pulses of random sequence (instead of square waves) but the rough tests strongly suggest that an amplifier gain control containing a linear velocity correction would compensate for the greatest bulk of the variability in voltage level.

5.23 - 5.26 DEPENDENCE OF PACKING AND VOLTAGE OUTPUT ON DURATION AND AMPLITUDE OF RECORDING PULSE.

As remarked earlier, information in the form of a sequence of binary voltage pulses may be identified and signalled by means of a binary cell, responding alike to all pulses exceeding in amplitude a certain threshold. Any scheme of identifying non-periodic message pulses in the presence of background noise must rely solely upon the amplitude-time characteristic of the individual message pulse, which must differ distinctly from that of the backgroundnoise. Various means for distinguishing such pulses from background noise may be proposed, involving both linear and non-linear operations on the combined message and noise; and at some later date this point will be discussed more fully. In the meantime, it may be remarked that if the message pulse can be maintained high in amplitude relative to the background noise, during some specific interval of time, the problem of identification becomes greatly simplified; and in nearly all schemes of pulse recognition amplitude discrimination plays a dominant role.

Accordingly, peak voltage amplitude may be taken as a crude measure of pulse interpretability, and phenomena such as that of "pulse overlap" may be said to destroy interpretability in proportion as they affect peak voltage amplitude. More specifically, the proximity with which pulses may be packed

the second of the opportunities of the second of the second of the second of

The second secon

on a wire can only be discussed in terms of the penalty paid in the form of "loss of interpretability", which may be taken as proportional to certain particularly specified losses in pulse amplitude.

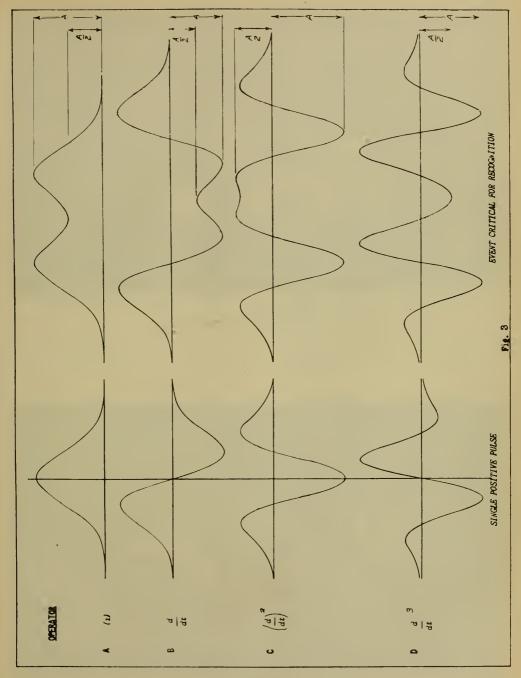

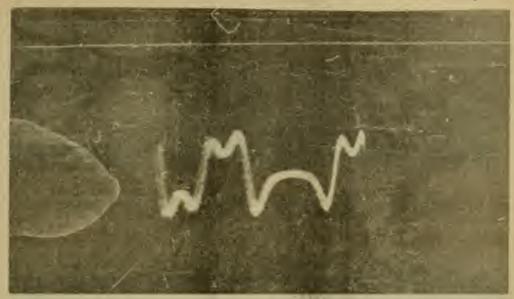

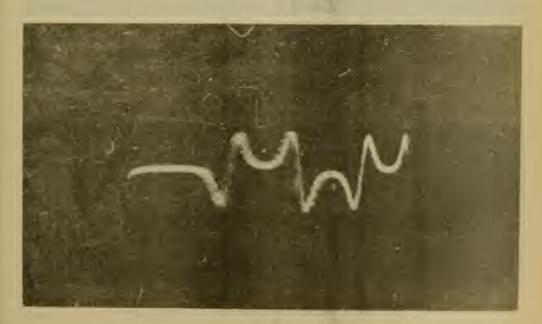

Consider the various forms into which the output voltage from the reading head may be cast (prior to interpretation), as indicated in Figure 3. If the voltage directly from the reading head is to be interpreted, the critical packing situation occurs when two pulses of opposite sign are adjacent; and the "Maximum safe packing" may be arbitrarily defined as that proximity at which the intervening discrimination valley has receded to one half peak pulse amplitude. Similar arbitrary amplitude thresholds of recognition may be set in the case of interpreting "differentiated" or "integrated" voltage waves, as indicated in Figure 3. An oscillogram showing actual overlap of voltage waves direct from the reading head, in the case of adjacent pulses of opposite sign, is shown in Figure 4A. These name pulses at a packing density corresponding to the arbitrary maximum of "one-half amplitude loss" in recognizability are indicated in Figure 4B.

Oscillograms of differentiated and integrated pulses are given in Figure 5, A, B, C.

Having in this manner established arbitrary standards of pulse interpretability, it becomes possible to investigate the pulse packing density which may be placed on various samples of magnetic recording wire which will afford "standard interpretability",

The maximum packing at "standard interpretability" depends not only upon duration of the recording current pulse, but also upon

Figure 3

Recording Head Output Voltages

Figure 4A Adjacent Voltage Pulses of Opposite Sign

Figure 4B Adjacent Voltage Pulses of Opposite Sign when

Output voltage direct from reading head. Three similar pulses spaced 141 to the inch. Recording pulse duration 8 microseconds, peak recording current 6.3 milliamperes.

Same pulses as above, restored by differentiation.

Same pulses as at top, restored by integration.

Figure 5 A, B, C.

Magnetic Wire Reproduced Wave Forms

recording current amplitude; and the reproduced voltage amplitude also depends upon these two factors. This relation was explored experimentally, using standard Brush heads and Brush BK No.913 wire. The apparatus used in this study consisted of the loop sample wire drive (4.1) and the recording driver (Section 7; also Diagram C-3-1009) which supplied current pulses of 8 to 800 microseconds duration to the head (waveform indicated in Figure 6B). For read-out purposes a pre-amplifier (Section 7; Diagram C-3-1010) was used in conjunction with a G.R. 714-A voltage amplifier; the output indicator being a Cathode Ray oscillograph,

A plot of the observed relationship between "recording current" and "maximum packing" for standard interpretability is represented in Figure 7.

This covers a range of pulse durations from 8 to 800 microseconds, and indicated a consistent increase (for all durations) in "maximum packing" as the recording current is reduced from about 12 to about 4 milliamperes. A "maximum" packing as high as 312 per inch results from pulses of 8 microsecond durations and 4 milliamperes recording current. It may also be seen that "maximum packing" increases constantly as pulse duration is reduced. (This family of curves, though as a whole consistent, is irregular in a few points, which may be attributed to error in observation of the C.R.O.).

In conjunction with the "Max packing" vs. "recording \*\*Trrent" plots of Figure 7 it may be of interest to examine the "voltage output" vs. "recording current" relationship. This is represented by Figure 8, which indicates that while the head output voltage decreases rapidly with reduced recording current for pulses of short duration, the output voltage is relatively unaffected by recording current change for longer pulse durations.

Figure 6

Register and Synchronizer Wave Forms

Maximum packing, pulses per inch

In fact, the recording current amplitude and duration conditions which produced lower "maximum packing" on Figure 7 appear to have produced voltage output pulses at the reading head which are relatively unaffected by changes in recording current from 4 to 12 milliamperes. Also, at lower recording currents, the maximum packing increases slightly but not abruptly. This suggests that it may be possible to explore experimentally the relationship between "maximum packing" and "voltage output" so as to find for each recording pulse amplitude and duration the highest output voltage at which the standard threshold of "maximum packing" is not violated. The results of this experimental attempt are presented in Figure 9 and seem to indicate that for BK 913 wire, all pulses having both relatively short durations (roughly 8 to 80 microseconds) and relatively low current amplitude (4 to 8 milliamperes) are roughly equivalent in their voltage output vs. packing density relationship.

Another relationship explored was that of peak voltage output at the reading head as a function of recording pulse duration; this is represented by Figure 10. It would appear that for Brush BK 913 wire moving 8.9 in/mc and excited by pulses of 7.5 milliamperes current, the peak voltage output at the reproducing head increases monotonically with duration of recording pulse, up to about 800 microseconds duration, and thereafter remains relatively constant.

## 5.28 COMPARATIVE PACKING OF WIRE SAMPLES

The most significant conclusion to be reached from the exploratory relationship presented in Figures 7-10 is that both the density of packing pulses and the voltage output of a given wire sample are related to each other and also to several other essential parameters; particularly, to recording pulse current and duration. Furthermore, it is clear that the system contemplated for pulse interpretation is a critical factor in judging the merits of any wire sample.

\_\_\_\_\_

Accordingly, a new comparison test was made between various samples of recording wire, the attempt being rade in each case to find the "Optimum" recording pulse duration and current amplitude so as to maximize the voltage output without falling below the packing factor for standard recognizability; the methods used being experimental adjustment as in the case of Figure 10.

The results of this survey are given on Table II for 17 samples of wire, for schemes of interpretation of (a) the direct voltage output, (b) integrated voltage, and (c) the differentiated voltage output. In each case the relative output voltage is cited, together with the standard "maximum" packing.

It may be seen that the Brush BK 913 wire tentatively adopted as standard by the I.A.S. project, ranks high in both "maximum packing" (218 per inch) and voltage output (150 microvolts per inch per second)

Comparative Tests of Magnetic Wires

|                         | Direct                        |                         |                      | Integrated              | in diameter of the contract of |                      | Difforontiated       | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |                        |

|-------------------------|-------------------------------|-------------------------|----------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------------------------|------------------------|

| Wire<br>Designation     | Recording<br>Current<br>(ma.) | Output<br>uv/in/<br>sec | A ½ lim.<br>Per inch | Output<br>uv/in/<br>sec | S 1/10 lim.<br>per inch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | S ½ lim.<br>per inch | Recording<br>Current | Output                                 | Lim.                   |

| GE Stainless A          | 29.2                          | 49                      | 83.4                 | 6.7                     | 82.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 139                  | 29.5                 | 5.8                                    | 187                    |

| Net'l Stand<br>No. 6630 | 18.3                          | 116                     | 133                  | 8.3                     | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 156                  | 5.0                  | 5.0                                    | 390                    |

| G E Steinlest C         | 14.2                          | 50.                     | 136                  | 4.16                    | 93.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 156                  | 3,3                  | 4.2                                    | S-3/4<br>312           |

| Stainless 46            | 9.16                          | 150                     | 130                  | 6.6                     | 93.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 156                  | 6.25                 | 10                                     | 234                    |

| Cunico No. 331          | 16.6                          | 215                     | 172                  | 11,7                    | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 218                  | 7.1                  | 11.7                                   | S− <del>½</del><br>390 |

| Cunife 1 No. 327        | 7 23.7                        | 300                     | 148                  | 16.5                    | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 188                  | 12.1                 | 50                                     | S-½<br>390             |

| BX 913 (Brush)          | 8.34                          | 150                     | 218                  | 6.7                     | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 250                  | 5.1                  | 12.5                                   | S-3/4<br>312           |

| G E 315                 | 20.0                          | 116                     | 156                  | 6.7                     | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 187                  | 8.3                  | 8                                      | S-3/4<br>250           |

| G E Carbon Steel        | 12.5                          | 183                     | 48.5                 | 29.8                    | . 43.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 62.5                 | 5.0                  | 7.5                                    | S-1<br>83.4            |

| Armour B614-6           | 15.0                          | 150                     | 48.5                 | 56.6                    | 9.07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59.3                 | 4.2                  | 4.2                                    | S-3/4<br>109           |

| Net'l Stend             | 10.8                          | 200                     | 57.8                 | 33.3                    | 48.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70.3                 | 5.84                 | ట                                      | S-3/4<br>106           |

| Brush BX906             | 8.3                           | 123                     | 78                   | 16.6                    | 73.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 109                  | 5.0                  | 5.0                                    | 218                    |

| Nat'l Stand             | 15                            | 83.5                    | 143                  | 5.0                     | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 180                  | 7.5                  | 5.8                                    | 390                    |

| Toro (Swedish)          | 20.8                          | 25                      | 359                  | 0.51                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      | 14.2                 | 2.5                                    | 5-3/4                  |

| E Stainless B           | 14.6                          | 13.3                    | 93.6                 | 1.03                    | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 133                  | 8,3                  | 1.03                                   | S-3/4<br>106           |

| E No. 176               | 22.9                          | 150                     | 108                  | 13.5                    | 90.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 140                  | 7.07                 | 8.34                                   | S-3/4<br>344           |

| Cunife D*               |                               | 80                      | 75                   | 1                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | l                    | ı                    |                                        | -\c\                   |

|                         |                               |                         |                      |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                      |                                        |                        |

12.

— <del>ग</del>

## VI. OUTER MEMORY COMPONENT (M2) DESIGN STUDIES

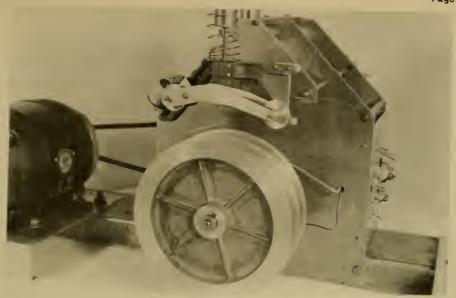

It was proposed (in the corresponding section of P.R. -1) that the High-Speed Wire Drive apparatus be modified so as to meet the requirements of the outer memory component M2. The basic principle of direct shaft drive to both loading and unloading reels was to be preserved, together with the scheme for differential servo slack takeup operating from a low inertia constant-tension loop follower. The main changes contemplated were:

- (1) To use particularly designed reels of smaller diameter (6 to 10 inches);

- (2) To provide a wire capacity of about 10 cubic inches;

- (3) To improve the servo design to extend the operating range up to speeds as high as possible;

- (4) To provide certain automatic features such as level winding, automatic parking brake, head engagement and adjustment, etc.;

- (5) To engineer the device with sufficient care and skill so that it would give trouble-free service under continual usuage.

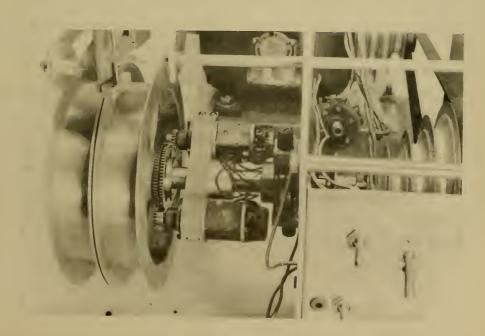

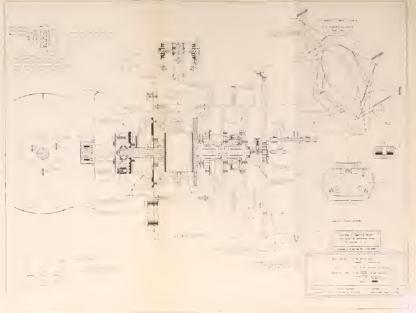

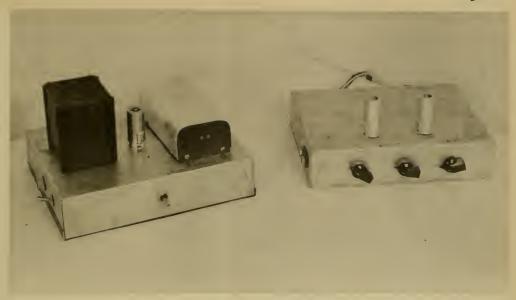

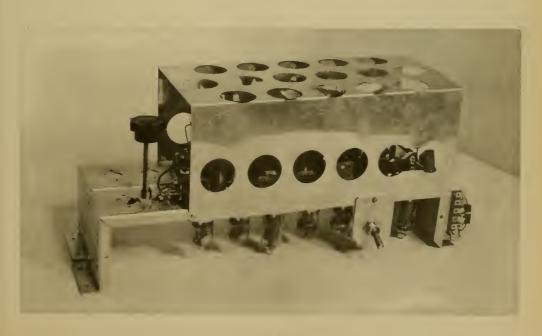

The first step in this development program was to design a true-scale plate model, having all essential parts in true dimension, but fabricated insofar as possible from standard catalogue parts and standard shapes, etc., avoiding the use of special castings, special motors and the cutting of special gears. Such a plate model was designed, constructed and tested in our model shop, and is pictured in Figures 11A and B. Three castings only were used: (1) the reels, of dural; and (2) the experimental servementor mount, of dural; and (3) the level-winding traverse beam, of magnesium alloy.

Although in the first "production" model of this component it is planned to use a servo-motor of the polyphase induction type, having double shaft takeoff to drive both reels, the plate model was built with two Delco internally-geared direct current permanent magnet motors, operating

Figure 11A

Plate Model, M2 Wire Drive showing Level Winder

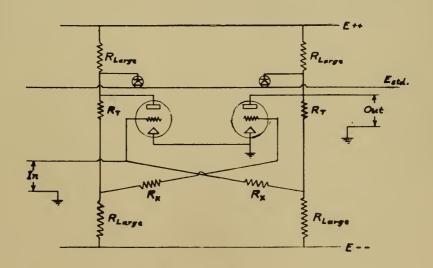

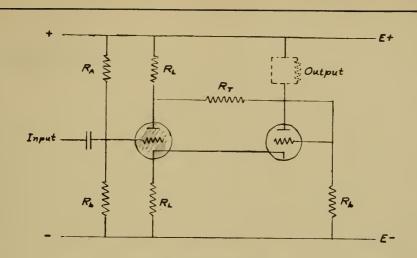

Figure ||B